文章內容

鐵電隨機存取記憶體(FRAM:Ferroelectric RAM)

❒ 鐵電效應(Ferroelectric effect)

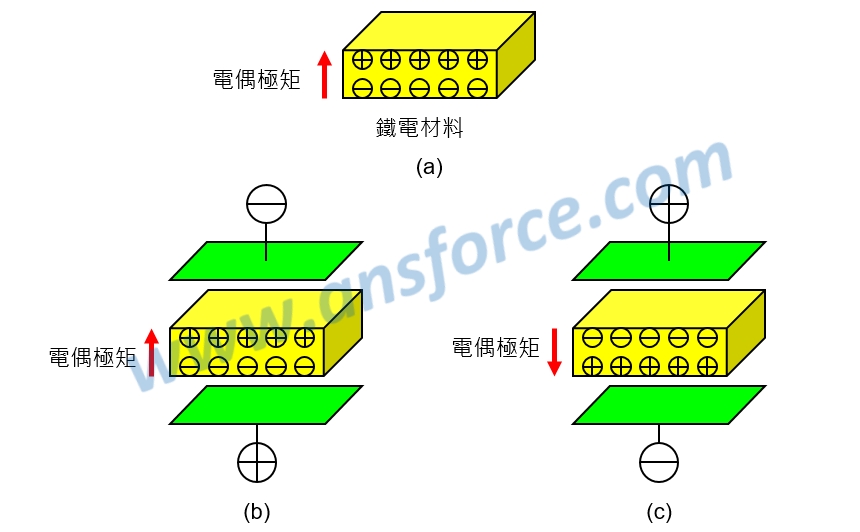

某些材料的晶體結構在不外加電場的情況下,就具有天然的「電偶極矩(Electric dipole moment)」,也就是固體材料的一端帶正電而另一端帶負電,如<圖一(a)>所示,這種材料稱為「鐵電材料(Ferroelectric materials)」,這類材料大多是陶瓷(金屬氧化物),例如:鈦鋯酸鉛(PZT:PbZrTiO3)、鉭鉍酸鍶(SBT:SrBiTa2O9)、鈦鍶酸鋇(BST:BaSrTiO3)等。科學家們發現,當我們外加電場,由於同性相斥、異性相吸,可以改變鐵電材料的電偶極矩(極化方向),如<圖一(b)與(c)>所示,這種現象稱為「鐵電效應(Ferroelectric effect)」。

電偶極矩(Electric dipole moment)是材料內一端帶正電而另一端帶負電所產生的,<圖一>中箭頭的方向代表材料帶正電的一端,其實和前面介紹極化光時提到的「極化方向(Polarized direction)」概念有點類似,別忘了,光波(電磁波)的電場方向稱為極化方向。

圖一 鐵電效應(Ferroelectric effect)示意圖。

❒ 介電常數(Dielectric constant)

絕緣材料的絕緣特性通常使用「介電常數(Dielectric constant)」的大小來代表,「K」就是指介電常數。

➤介電常數大(High K)的絕緣材料:代表這種絕緣材料容易吸引電子與電洞,所以適合用來製作「電容」,因為電容原本就是用來吸引(儲存)電子與電洞的。

➤介電常數小(Low K)的絕緣材料:代表這種絕緣材料不容易儲存電子與電洞,所以適合用來製作積體電路(IC)內多層導線之間的「絕緣層」,這樣電子才可以在多層導線之間自由流動而不會被吸引(儲存)。

❒ MESFET結構的鐵電隨機存取記憶體(FRAM)

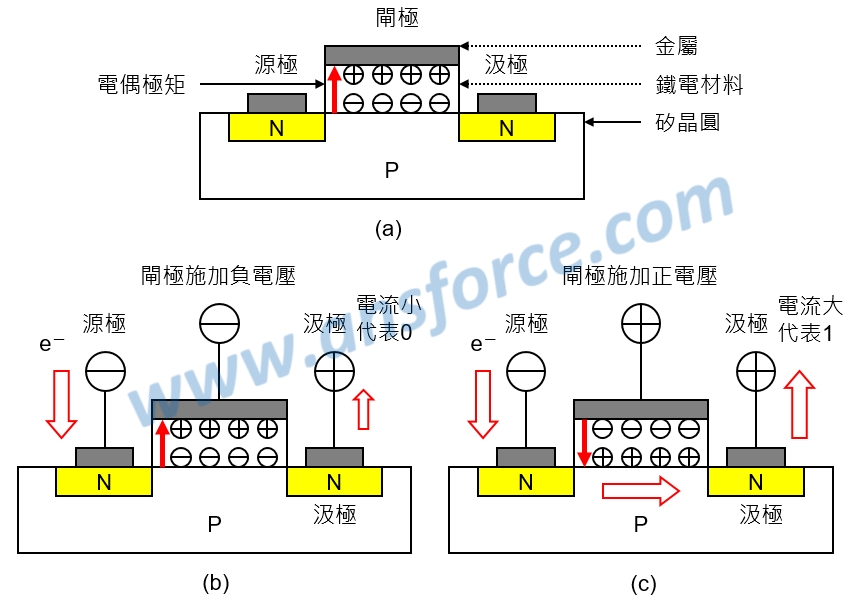

在中央P型矽晶圓上方成長一層鐵電材料薄膜,再成長一層金屬薄膜,形成「金屬-鐵電-半導體」的結構,如<圖二(a)>所示。

➤寫入資料0:閘極施加負電壓,使鐵電薄膜的「電偶極矩」向上代表寫入0。

➤寫入資料1:閘極施加正電壓,使鐵電薄膜的「電偶極矩」向下代表寫入1。

➤讀取資料0:鐵電薄膜的電偶極矩向上時,由源極通入電子無法流到汲極,造成汲極電流比較小,代表讀取0,如<圖二(b)>所示。

➤讀取資料1:鐵電薄膜的電偶極矩向下時,由源極通入電子可以流到汲極,造成汲極電流比較大,代表讀取1,如<圖二(c)>所示。

圖二 MFSFET結構的鐵電隨機存取記憶體示意圖。

❒ DRAM結構的鐵電隨機存取記憶體(FRAM)

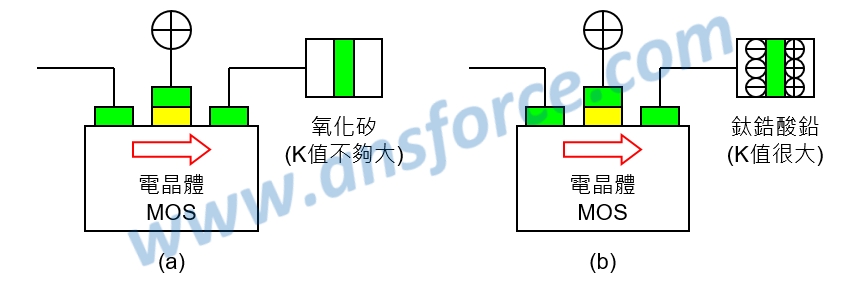

顧名思義就是使用動態隨機存取記憶體(DRAM)的結構,使用一個電晶體(MOS)與一個電容來儲存一個位元(bit)的資料,由於傳統DRAM的電容都是使用「氧化矽」做為絕緣體,如<圖三(a)>所示,氧化矽的介電常數不夠大(K值不夠大),因此不容易儲存電子與電洞,造成必須不停地補充電子與電洞,所以稱為「動態(Dynamic)」,只要電腦的電源關閉,電容所儲存的電子與電洞就會流失,DRAM所儲存的資料也就會流失。

FRAM是使用「鈦鋯酸鉛(PZT)」與「鉭鉍酸鍶(SBT)」這種介電常數很大(K值很大)的鐵電材料來製作電容,如<圖三(b)>所示,如此就很容易儲存電子與電洞而不會流失,不需要補充電子與電洞,就算電腦的電源關閉資料也不會流失了,不過要將鈦鋯酸鉛(PZT)與鉭鉍酸鍶(SBT)這種材料製作在矽晶圓上目前只能使用「濺鍍法(Sputter)」,而且這種成份複雜的化合物成長薄膜的技術仍然不夠成熟,所以良率較低。

圖三 DRAM結構的鐵電隨機存取記憶體示意圖。

❒ 鐵電隨機存取記憶體(FRAM)的優缺點

➤優點

1.屬於「非揮發性記憶體(NVM)」,電源關閉後資料仍然可以保存。

2.不像快取記憶體(Flash ROM)需要高電壓強迫電子注入浮動閘極,所以耗電量較低。

3.不像硬碟機(HDD)需要使用旋轉馬達與讀取頭,所以很省電、耐撞擊、不跳針。

➤缺點

1.必須使用「鈦鋯酸鉛(PZT)」與「鉭鉍酸鍶(SBT)」這種特別的材料,製程不夠成熟,良率較低。

2.許多專利由國外公司掌握,如果支付專利費用,則生產成本較高,售價也較高。

【請注意】上述內容經過適當簡化以適合大眾閱讀,與產業現狀可能會有差異,若您是這個領域的專家想要提供意見,請自行聯絡作者;若有產業與技術問題請參與社群討論。

【延伸閱讀】其他詳細內容請參考「積體電路與微機電產業,全華圖書公司」。<我要買書>