文章內容

Wire Bonding

❒ Process of wire bonding

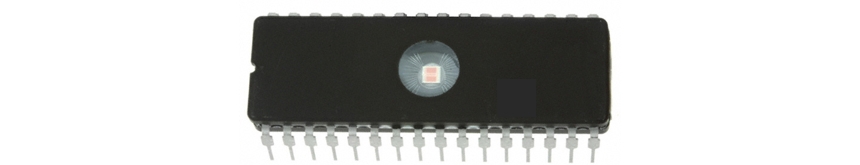

Wire bonding utilizes “lead frame” and “gold wires,” and needs to make the bond pad around the chip. The metal pins of lead frame must be made around the IC package case, as shown in Fig. 1, and thus the number of pins for wire bonding cannot be too many. The process of wire bonding includes: on the side near the chip, utilizing mechanical capillary to heat and press the gold wires onto the bond pad around the chip; and, on the side near the lead frame, utilizing mechanical capillary to heat and press the gold wires onto the lead frame; after finishing the first gold wire, continuing on the first gold wire, and so on.

Figure 1: Wire bonding.

The biggest disadvantage of wire bonding is that the operation of wire bonding must be processed one wire by one wire and it is very time consuming. Besides, if the number of CMOS in a chip becomes more, the transmitting electric signals become more and the required gold wires become more. However, the space around the chip is limited and can only accommodate a fixed number of bond pads; and, the space around the packaging case is also limited and can only accommodate a fixed number of metal pins, so the number of pins for wire bonding will not be too many.

❒ Applications of wire bonding

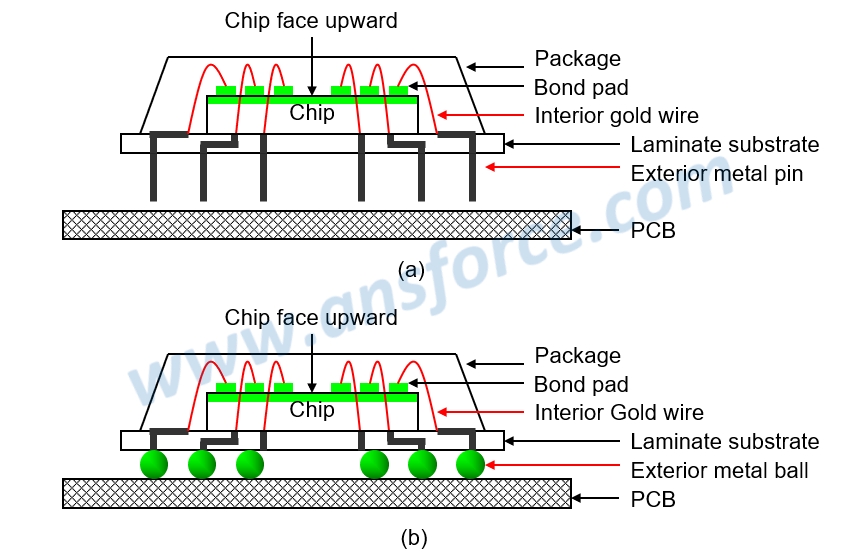

Except of lead frame, the wire bonding can also utilize the “laminate substrate,” as shown in Fig. 2. The package exterior using Pin Grid Array (PGA) or Ball Grid Array (BGA) is described as follows:

➤ Wire bonding for interior and PGA for exterior: As shown in Fig. 2(a), this packaging method was often applied for Intel CPU before, but now most of them utilize flip-chip package instead.

➤ Wire bonding for interior and BGA for exterior: As shown in Fig. 2(b), this packaging method was often applied for Northbridge chip and Southbridge chip of personal computer, but now most of them utilize flip-chip package instead.

Figure 2: Applications of Wire bonding.

❒ Advantage/Disadvantage of wire bonding

➤ Advantage: Suitable for middle and small chips, but also some large chips; and, the technology is more mature.

➤ Disadvantage: Each pin must be wire bonded, so the packaging speed is slower and the package volume will be larger.

【Remark】The aforementioned contents have been appropriately simplified to be suitable for reading by the public, which might be slightly differentiated from the current industry situation. If you are the expert in this field and would like to give your opinions, please contact the writer. If you have any industrial and technical issues, please join the community for further discussion.