文章內容

邏輯設計(Logical design)

❒ 邏輯設計的定義

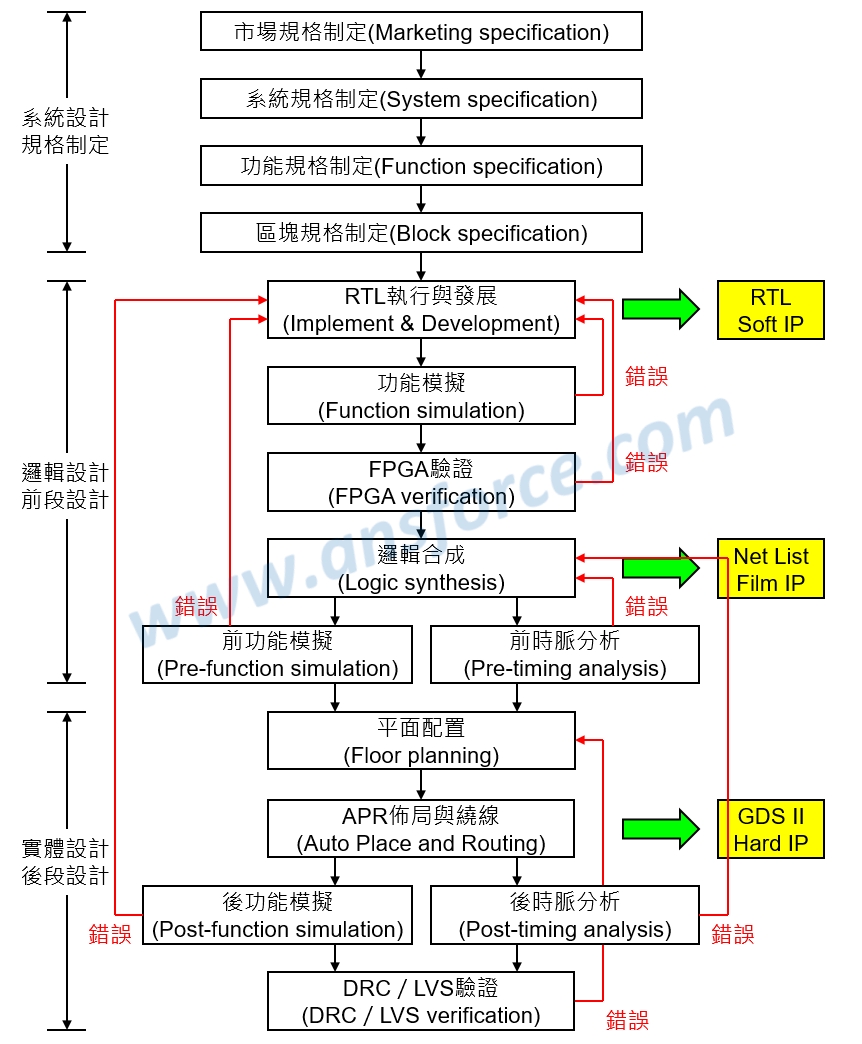

邏輯設計的主要工作是將積體電路所需要的邏輯順序表示出來,規格制定主要包括五個部分:RTL執行與發展、功能模擬、FPGA驗證、邏輯合成、前功能模擬與前時脈分析,詳細的設計流程如<圖一>所示。

圖一 數位積體電路的設計流程。

❒ RTL執行與發展(Register Transfer Level Implement & Development)

「語法轉換層次(RTL:Register Transfer Level)」是指將硬體描述語言中所使用的邏輯語法,轉換成相同邏輯意義的「邏輯閘(Gate)」。IC設計工程師使用硬體描述語言(Verilog或VHDL),將積體電路所需之邏輯以程式明確地描述每個區塊的內部功能,所得到的結果如<圖二(a)>所示,稱為「RTL程式碼(RTL code)」,類似電腦工程師使用程式語言(BASIC或C語言)來撰寫應用程式(例如:Windows或Word)。RTL程式碼是一個具有價值的設計結果,也是重要的智慧財產權(IP),我們稱為「Soft IP」,大家應該也猜得到,因為它實在很像一個軟體(Software)程式,所以稱它為「Soft」。

<圖二(a)>為IC設計工程師使用VHDL硬體描述語言所撰寫的程式內容,目的在設計一個具有4個輸入端與1個輸出端的多工器,如<圖二(b)>所示,仔細看看程式內容中有些什麼?Begin…If…Then…Else…End,是不是覺得與大學一年級時計算機概論課程中使用BASIC或C語言撰寫的軟體程式很像呢?雖然硬體描述語言與軟體程式內容很像,但是兩者所代表的意義完全不同。因為一般的軟體程式(BASIC或C語言)只要語法邏輯正確便可以成功執行,但是硬體描述語言(Verlog或VHDL)不只是語法邏輯必須正確,還必須能夠轉換成相同邏輯意義的「邏輯閘(Gate)」才行,由於軟體程式與硬體描述語言並不相同,IC設計工程師除了會使用軟體語言之外(資訊工程背景),更重要的是電子電路的概念(電機工程背景),因此必須由電子電機相關科系畢業的工程師才能勝任。

.jpg)

圖二 邏輯設計的範例。(a)RTL程式碼;(b)多工器電路。

❒ 功能模擬(Function simulation)

IC設計工程師使用硬體描述語言(Verilog或VHDL),將積體電路所需之邏輯以程式明確地描述每個區塊的內部功能以後,接著使用電腦軟體進行「功能模擬(Function simulation)」,若正確則繼續進行下一步「FPGA驗證」,若錯誤則從新回到「RTL執行與發展」,如<圖一>所示。硬體描述語言的功能模擬類似電腦工程師使用編譯器(Complier)來對撰寫好的程式進行除錯(Debug)的動作,如果發現錯誤則從新修改程式,如果正確則將程式轉換成機器碼。

❒ FPGA驗證(FPGA verification)

現場可程式化邏輯陣列(FPGA:Field Programmable Gate Array)晶片是由大量的AND閘與OR閘與EEPROM排列組合而成的積體電路(IC),完成功能模擬後,將RTL程式碼(RTL code)以電訊號寫入(燒錄)到FPGA晶片中,由於FPGA晶片類似真實的晶片,因此燒錄程式後的FPGA晶片可以當作真實的晶片連接到系統中進行實機測試,若正確則繼續進行下一步「邏輯合成」,若錯誤則從新回到「RTL執行與發展」,如<圖一>所示。

FPGA晶片的價格是由所設計積體電路(IC)的複雜程度來決定,所設計的積體電路(IC)愈複雜,所含邏輯閘愈多,需要的FPGA晶片愈複雜,價格愈高。由於一般FPGA晶片時脈頻率只能達到大約500MHz,但是真實的晶片工作頻率常常超過500MHz,例如:處理器(CPU或ARM)的工作頻率一般都在1GHz以上,這麼高的頻率就無法使用FPGA驗證。使用FPGA驗證的優點是可以連接到系統中模擬真實的晶片來測試其正確性;缺點是只能測試晶片在時脈頻率小於500MHz的情形。IC設計時所使用的FPGA晶片構造複雜,其設計與製造的廠商多為國外大廠,例如:Altera(亞爾特拉)、Xilinx(賽靈思)、Lattice(萊迪斯)等公司。

❒ 邏輯合成(Logic synthesis)

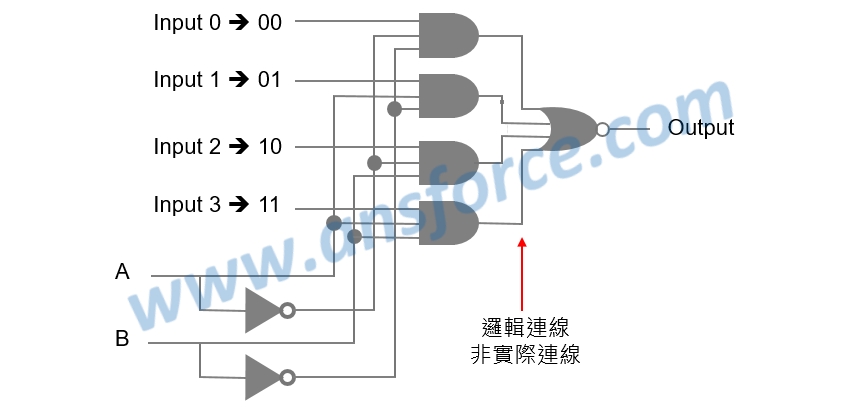

IC設計工程師將撰寫好的RTL程式碼(RTL code),載入邏輯合成所使用的電子設計自動化工具(EDA tool),經過電腦輔助設計將「RTL程式碼」轉換成相對應的「邏輯閘(Gate)」,電腦會自動依照RTL程式碼的設定完成相對應的「邏輯閘位置」與「邏輯連線」,得到如<圖三>的邏輯設計圖。邏輯設計圖是一個具有價值的設計結果,也是重要的智慧財產權(IP),稱為「Firm IP」。邏輯合成所使用的電子設計自動化工具很多,常見的有:益華科技(Candence)所銷售的「Encounter RTL Compiler」、新思科技(Sysnopsys)所銷售的「Design Complier」等。

圖三 多工器電路轉換出來的邏輯電路圖。

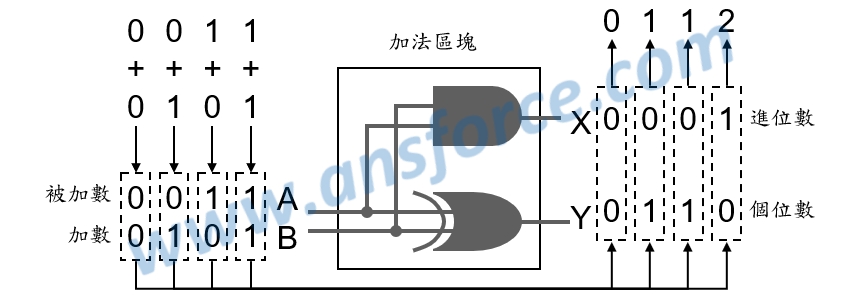

<圖三>所示的邏輯設計圖,其是就是將許多邏輯閘連接起來,以達成我們所需要的運算工作,所謂的「邏輯閘位置」與「邏輯連線」是指邏輯設計圖上如何將不同的邏輯閘連接起來,並不是真正在矽晶片上電晶體(CMOS)的實際位置與實際連線。大家可以自行比較<圖三>與<圖四>,它們都是由不同的邏輯閘(Gate)排列組合而成的圖形。大家別忘了,邏輯閘是數個電晶體(CMOS)排列組合而成,因此在IC設計的最後一步「實體設計(Physical design)」才會將所有的邏輯閘都轉換成電晶體(CMOS),這個時候才會將這些電晶體(CMOS)真正配置在矽晶片上的「實際位置」,再使用金屬導線連接起來形成「實際連線」。

圖四 利用邏輯閘運算0+0=00(代表十進位的0)、0+1=01(代表十進位的1)、1+0=01(代表十進位的1)與1+1=10(代表十進位的2)。

❒ 前功能模擬與前時脈分析

➤前功能模擬(Per-function simulation):主要在驗證上述邏輯閘位置與邏輯連線是否正確,如果正確則進行下一步「實體設計」;如果錯誤則返回「RTL執行與發展」重新修改程式,如<圖一>所示。

➤前時脈分析(Per-timing analysis):主要在驗證上述邏輯閘位置與邏輯連線是否可以在產品所要求的工作頻率下正確地運作,如果可以則進行下一步「實體設計」;如果錯誤則返回「邏輯合成」重新修改邏輯閘位置與邏輯連線。

【延伸閱讀】以上詳細內容請參考「積體電路與微機電產業」。<我要買書>