文章內容

多層導線技術(Multi metal layer)

❒ 多層導線的製作

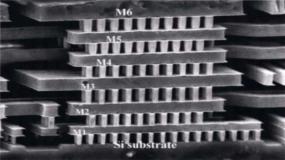

積體電路中的CMOS其實只是「地下室」,最重要的是將這些CMOS「連接起來」,最後會形成如<圖一>的多層導線結構,假設圖中方框圈起來的部分是MOS,其上方堆疊了一層一層的銅薄膜,由下而上依序稱為Metal 1(簡稱M1)、Metal 2(簡稱M2)、Metal 3(簡稱M3)…等等。金屬的材料種類在早期是使用鋁,稱為「鋁製程(Aluminum process)」,鋁的熔點較低容易製作,但是低熔點的金屬容易受到某些高溫的製程破壞,也容易被積體電路使用時所產生的高溫與電子破壞,因此目前晶圓廠大都使用「銅製程(Copper process)」,金屬銅的熔點較高不易製作,但是由於半導體製程技術的進步,目前銅製程已經相當成熟。

圖一 積體電路的多層導線結構。

資料來源:聯華電子(UMC)。

❒ Low K材料

此外,各層金屬之間必須以絕緣材料隔開,這種絕緣材料又稱為「Low K材料」,一般都是由不導電的陶瓷材料或高分子材料(塑膠)組成,<圖一>中各層金屬之間看起來沒有任何物質,好像是「空心的」,其實那是為了要拍攝出有立體感的電子顯微鏡照片而故意將晶圓放在化學藥品中浸泡,將Low K材料溶解以後所造成的,原本在各層金屬之間是「實心的」Low K材料。請大家記得,這些金屬柱子的寬度都大約只有0.1μm(實際的寬度要視晶圓廠的製程線寬而定),所以金屬與金屬之間不可能是空心的,否則很容易因為使用者不小心讓電子產品撞了一下,就把積體電路內所有的導線「震垮」了。

在<圖一>中可以看出各層金屬之間在垂直方向上有「金屬柱」連接起來,這些金屬柱稱為「VIA」或「Plug」,主要的功能是讓電子可以沿著金屬柱在不同金屬層之間流動,至於這麼複雜的多層導線結構是怎麼製作的?仍然是反覆使用黃光微影、薄膜成長、蝕刻技術等步驟製作而成。

❒ 介電常數(Dielectric constant)

絕緣材料的絕緣特性通常使用「介電常數(Dielectric constant)」的大小來代表,上面所提到的「K」就是指介電常數。知識力www.ansforce.com。

➤介電常數大(High K)的絕緣材料:代表這種絕緣材料容易吸引電子與電洞,所以適合用來製作「電容」,因為電容原本就是用來儲存(吸引)電子與電洞的。

➤介電常數小(Low K)的絕緣材料:代表這種絕緣材料不容易吸引電子與電洞,所以適合用來製作積體電路(IC)內多層導線之間的「絕緣層」,這樣電子才可以在多層導線之間自由流動而不會被吸住。

前面曾經介紹過,隨機存取記憶體(DRAM)中,要儲存一個位元(bit)的資料(一個0或一個1),是由一個CMOS與一個電容來達成,由於一般DRAM的電容都是使用氧化矽製作,氧化矽的介電常數不夠大(K值不夠大),因此不容易吸引電子與電洞,造成必須週期性地補充電子與電洞,故稱為「動態(Dynamic)」,只要電源關閉,電容所儲存的電子與電洞就會流失,DRAM所儲存的資料也會流失。目前有一種記憶體稱為「鐵電隨機存取記憶體(FRAM:Ferrielectric RAM)」,就是使用鈦鋯酸鉛(PZT)與鉭鉍酸鍶(SBT)這種介電常數很大(K值很大)的絕緣材料來製作電容,如此就很容易吸引電子與電洞而不會流失,就算電源關閉資料也不會流失,就好像隨身碟(快閃記憶體)一樣,不過鈦鋯酸鉛(PZT)與鉭鉍酸鍶(SBT)這種鐵電材料製作在矽晶圓上的技術仍然不成熟,單價也比較高,因此無法製作大容量的記憶體來取代快閃記憶體或DDR。

❒ 多層導線概念

假設「地下室」只有6個CMOS要用銅導線連接起來,如<圖二(a)>所示,C1與C2連接、C3與C4連接、C5與C6連接,要如何連線最節省空間呢?

➤方法一:如<圖二(b)>所示,只使用一層銅導線,由於不同的銅導線不能碰在一起,否則會短路而燒毀CMOS,因此所有的銅導線只能繞道而行,如果地下室有一百萬個CMOS,那麼會繞成多麼複雜的線路大家可想而知囉!知識力www.ansforce.com。

➤方法二:如<圖二(c)>所示,使用三層銅導線,C1與C2由第一層銅導線(M1)連接,C3與C4由第二層銅導線(M2)連接,C5與C6由第三層銅導線(M3)連接,各層金屬之間以絕緣材料(Low K)隔開,因此各層金屬之間並不會短路,如此一來就不會有複雜的線路了。

圖二 積體電路的多層導線結構。

多層導線架構主要的功能是要將「地下室」的數百萬個CMOS連接起來,想像一下,地下室總共有數百萬個CMOS,如果只使用一層銅導線,顯然線路會非常複雜,而且必須要很大的面積才夠(可能要將數百萬個CMOS分散開來才行),這樣會造成晶片面積變大,因此使用多層導線不但可以使線路變得比較簡單,也可以讓晶片保持原來的面積大小(不需要將數百萬個CMOS分散開來)。至於積體電路(IC)到底需要多少層導線(Metal)必須視積體電路本身的複雜程度而定,換句話說,要看一個晶片內有多少個CMOS來決定,CMOS愈多代表這個晶片愈複雜,功能愈強,需要愈多層導線,以Intel公司的Penitum IV處理器為例,大約使用10層導線製作,而IBM公司也宣稱他們在實驗室成功製作出21層導線,將來要在矽晶片上製作「101大樓」也是指日可待的了,但是每增加一層金屬導線就會增加至少兩道光罩,其中一道光罩用來決定low K材料那些位置需要鑽孔,一道光罩用來決定金屬導線的位置,這代表會增加成本與製作的困難度。

❒ 積體電路製作所需的光罩數目

一般晶圓廠完成一片矽晶圓的製作要使用多少道光罩呢?本書中的NMOS只使用了3道光罩就製作完成,但是一般晶圓廠所生產的CMOS大約需要8道光罩,再加上CMOS上方可能要製作多層導線將數百萬個CMOS連接起來,因此總共需要大約20道光罩才夠,線寬只有0.1μm(目前最小只有20nm),要將這20道光罩對得很準實在不是一件容易的事。而在晶圓廠中,每一道光罩放在曝光機(步進機)內由紫外光投射到矽晶圓以後,還要經過高溫氧化、摻雜技術、蝕刻技術與薄膜成長等化學或物理程序,才能完成「一道光罩」的相關製造工作,這一連串的製造程序大約需要3天的時間,換句話說,在晶圓廠中每一道光罩大約需要3天的時間才能完成相關的製造程序,如果一個矽晶圓總共需要20道光罩,則送進晶圓廠大約需要60天(20道光罩⨯3天)的時間才能製造完成。知識力www.ansforce.com。

【請注意】上述內容經過適當簡化以適合大眾閱讀,與產業現狀可能會有差異,若您是這個領域的專家想要提供意見,請自行聯絡作者;若有產業與技術問題請參與社群討論。

【延伸閱讀】其他詳細內容請參考「積體電路與微機電產業,全華圖書公司」。<我要買書>

【文章圖示】聯華電子(UMC)。